## Fundamental

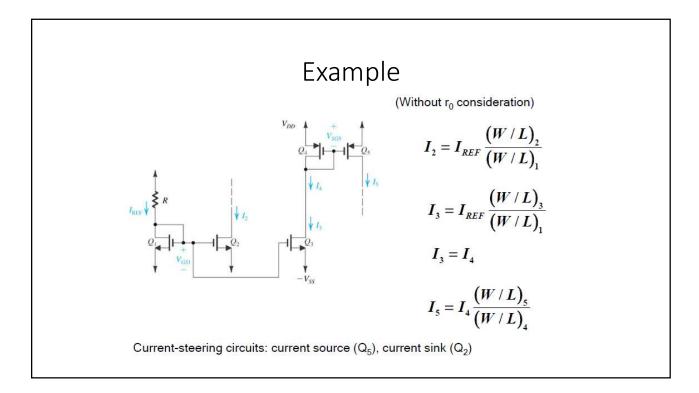

- Biasing in integrated-circuit design is based on the use of constantcurrent sources.

- On an IC chip with a number of amplifier stages, a constant dc current (called a **reference current**) is generated at one location and is then replicated at various other locations for biasing the various amplifier stages through a process known as **current steering**.

- This approach has the advantage that the effort expended on generating a predictable and stable reference current, usually utilizing a precision resistor external to the chip or a special circuit on the chip, need not be repeated for every amplifier stage.

- The bias currents of the various stages track each other in case of changes in power-supply voltage or in temperature.

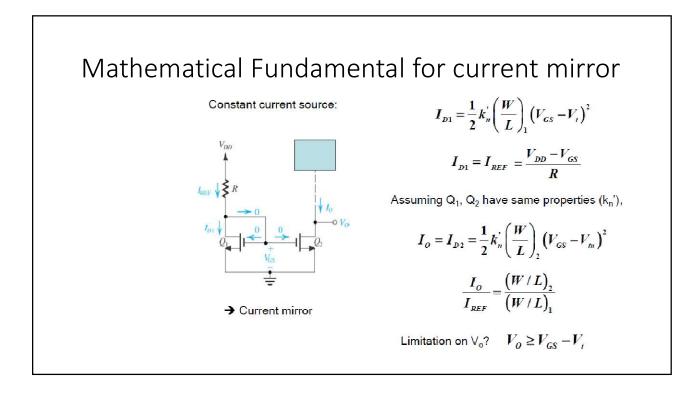

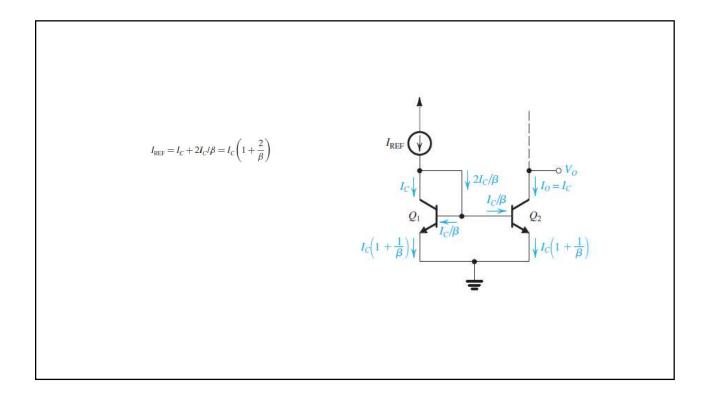

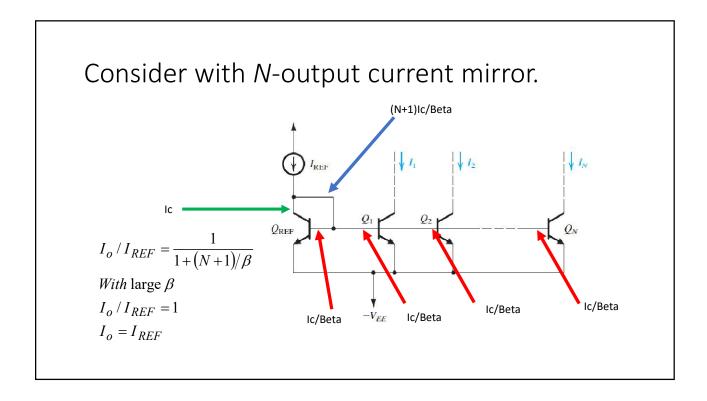

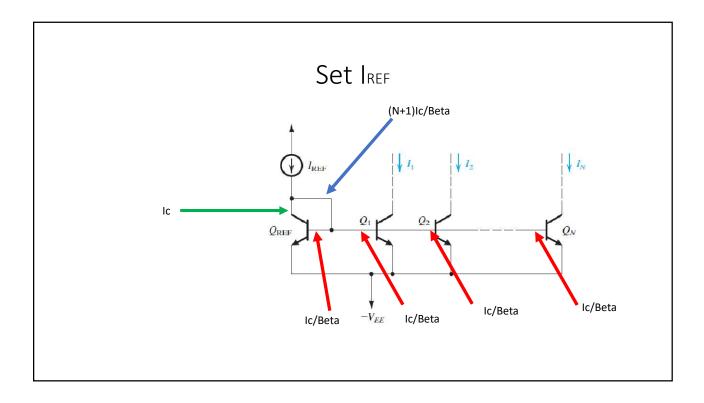

Finally, since  $I_0 = I_c$ , the current transfer ratio can be found as

$\frac{I_O}{I_{\text{REF}}} - \frac{I_C}{I_C \left(1 + \frac{2}{\beta}\right)} - \frac{1}{1 + \frac{2}{\beta}}$

Note that as  $\beta$  approaches  $\infty$ , *Io* //REF approaches the nominal value of unity. For typical values of  $\beta$ , however, the error in the current transfer ratio can be significant. For instance,  $\beta = 100$  results in a 2% error in the current transfer ratio. Furthermore, the error due to the finite  $\beta$  increases as the nominal current transfer ratio is increased.

## Just for student's understanding

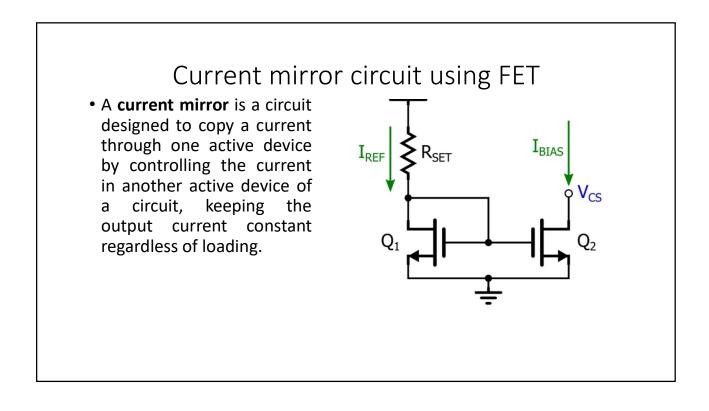

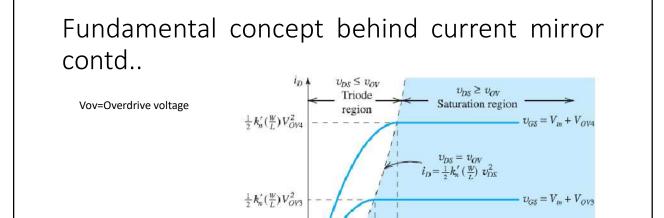

- As you can see, the drain of  $Q_1$  is shorted to its gate. This means that  $V_G = V_D$ , and thus  $V_{GD} = 0$  V. So, is  $Q_1$  in cutoff, the triode region, or the saturation region? It can't be in cutoff, because if no current were flowing through the channel, the gate voltage would be at  $V_{DD}$ , and thus  $V_{GS}$  would be greater than the threshold voltage  $V_{TH}$  (we can safely assume that  $V_{DD}$  is higher than  $V_{TH}$ ). This means  $Q_1$  will always be in saturation (also referred to as "active" mode), because  $V_{GD} = 0$  V, and one way of expressing the condition for MOSFET saturation is that  $V_{GD}$  must be less than  $V_{TH}$ .

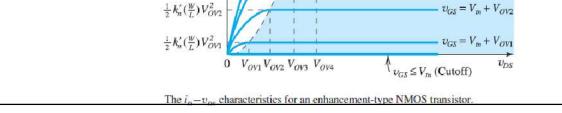

- If we recall that no steady-state current flows into the gate of a MOSFET, we can see that the reference current  $I_{REF}$  will be the same as  $Q_1$ 's drain current. We can customize this reference current by choosing an appropriate value for  $R_{SET}$ . So what does all this have to do with  $Q_2$ ? Well, the drain current of a MOSFET in saturation is influenced by the width-to-length ratio of the channel and the gate-to-source voltage.

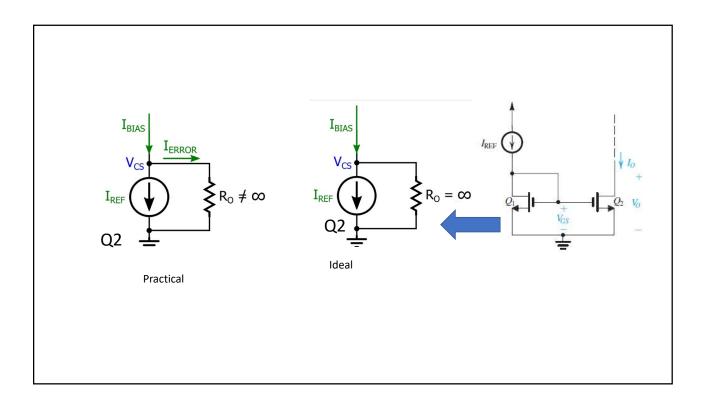

• Now notice that both FETs have their sources tied to ground and that their gates are shorted together—in other words, both have the same gate-to-source voltage. Thus, if we assume that both devices have the same channel dimensions, their drain currents will be equal, *regardless of the voltage at the drain of Q*<sub>2</sub>. This voltage is labeled V<sub>CS</sub>, meaning the voltage across the current-source component; this helps to remind us that Q<sub>2</sub>, like any well-behaved current source, generates a bias current that is not affected by the voltage across its terminals. Another way to say this is that Q<sub>2</sub> has infinite output resistance: